# A High Flexible Low-Latency Memory Based 5g Fft Processor

# T. Kalpana<sup>1</sup>, Vadalasetty. Yaswanth Naveen<sup>2</sup>, Y.Manasa<sup>3</sup>, N.Naveen Reddy<sup>4</sup>,

### B.Himavardhan Reddy<sup>5</sup>.

<sup>1</sup>assistant Professor In Dept Of Ece In Lakireddy Bali Reddy College Of Engineering, L.B.Reddy Nagar, Krishna District, Mylavaram, Andhra Pradesh 521230.

<sup>2, 3, 4, 5</sup> B.Tech In Dept Of Ece In Lakireddy Bali Reddy College Of Engineering, L.B.Reddy Nagar, Krishna District, Mylavaram, Andhra Pradesh 521230.

Abstract: Fourier fast transform (FFT) is a programmable high-throughput processor intended to handle 16- through 4096-point FFT and 12 to 2400-point discrete 4G, wireless local area and future 5G transformers (DFTs). As an agreement between performance and costs, a 16-path data parallel architecture is chosen for the memory. Several enhancements have been made to build a hardware-efficient high-speed CPU. A reconfigurable butterfly unit, comprising eight parallel to radix-2, four parallel to radix-3/4, two parallel to radix-5/8 and one radix-16, is suggested to enable computation for optimum use of hardware resources. Twiddle factor multipliers are improved and compared with various methods. Finally, modified co-ordinate rotation is developed to reduce hardware costs while enabling both FFTs and DFTs. An optimal conflict-free access method for numerous butterflies is also proposed at all roots. The processor may be implemented using a processor synthesiser and designed as an IP (applicationspecific instruction-set processor designer).

# KEYWORDS: FAST FOURIER TRANSFORM; FFT; KERNEL; MIMO; OFDM; MULTI STANDARD.

## 1. Introduction

Symmetrical multiplexing recurrence division (OFDM) is one of the similar communication approaches, particularly when the data negotiation frame rate is too high. It has been chosen as a compliance consultant for IEEE 802.11a[2], ultra-wideband[3], long-run [4], and video-to-terrestrial digital [5]. FFT operation is the primary function of OFDM. Furthermore, Kuli-Turki algorithm[6] is also the most frequently used FFT. Divide and beat any compound length n recursively. The FFT processor's discrete Fourier transformation needs many impredictable increments, though. The computation using Radix4 is gone, but it requires a more complicated four-factor butterfly block. I believe in [7-10], which lowers the complexity of raising the issue of jitter computations, that FFT, Radix24 and Radix2k are included. Improvements in FFT design conceal themselves as greater performance and lower system complexity, while decreasing pressure utilisation and speed. The basic memory-based FFT model ([11]) consists of recurrent components (butterfly blocks), memory devices and runtime libraries. The most popular versions are the memory-based ones. However its equipment and physical expenses are cheaper than exclusive designs, and frequently owing to its capacity to deal with objects and memory, performance and inertia are reduced. Thus, a directed FFT circuit to compute the FFT to satisfy the expanded application runtime requirements is suggested by the equipment designer. These channel models may provide large returns compared to the near real costs that are appropriate for continuous usage. Thanks to the FFT channel structure, the input and power scheme are medium and wide. The structure of the first feeding is described in its late manifestation, i.e. H. For all courses, accurate planning, relocation and delivery of recording components are carried out. These models may be separated into one-mode, SDC and Multi-User Mode Transmission Switches (MDC)[12], in the following higher-level models. [13]. The control block for the SDC engineering is uncertain. The MDC design needs to take longer time on the high motherboard, but it may produce extra samples. The structure produced by MDF[13] needs greater storage space and facilities compared to the one manufactured by SDF. MIMOOFDM enables multiplexing input, multimedia and cyclic symmetry and performs better than distant 4G and 5G stations. Several radio and symmetrical repeating departments send distinct messages, and various communication

ISSN: 2233-7857IJFGCN Copyright ©2021SERSC frameworks are not attractive. While pantomime utilises a mix of abnormal time and rigorous code entry for the department, the preoccupation with ofdm is well recognised for its data congestion, high communication, constraints and excessive performance. Consequently, some common services are inherent in the LAN cables and switches. The memory length also grows quickly when stats grow using mdc-based mimoofdm, but multi-way delay switches manage wi statistics in the most honest manner. The DM-based pantomime rule is because it is simple, and customer data are tightly divided into a restricted department to eliminate further barriers to continuous development.

# LITERATURE REVIEW

E. G. Larsson et al. [1] "Large MIMO" implies an essential component to reduce matching frameworks in aspect. The wide capability of "Massive MIMO" frames is a key factor in innovation that enables the approach beyond the 4G cell and thrown frames. In this article. This frame was designed to provide unrivalled production, high-quality electricity and efficiency. In this reference, S. Liu and D. Liu[2] are mainly aimed at an overly efficient "Speedy Fourier Programmable Restructuring Processor" (P-FFT) to assist variable Fourier adaptations and Fourier transformations (DFTs). Minotta[3] and Al. This article offers a few methods of inspiring adaptable ftt maintained an approximate age track for FPGA implementation. The calculation is familiar and the system reproducing the FFT radix-2 fidget elements ignores the number of focal points, collapsing problem. In this context, the FFT(rampid Fourier exchange) was particularly focused on spherical design, and could achieve complete system butterfly skill and none of its supplements was further reduced to 1/2 [4]. Wen-Chang Yeh[5] spoke about a split radix short pipeline engineering design for the pipeline exchange Fourier (SRFFT) in the article. They have made the Cooley–Tukey calculations, which have mainly been completely relied on, to plan it really is standard for any point of 2^n. SDC-SDF (unmarried route commutator-feedback) is a high-performing consolidated radix-2 pipeline for fast transforming Fourier (FFT) architecture with log2N-1 SDC levels and 1 SDF level[6].

# EXISTING SYSTEM:

In the true layer of the Symmetrical Recurrence Multiplexing Department (OFDM) architecture for trading statistics in a temporal and recurrent region, Fast Fourier Transform (FFT) is the signed escalated computation. The 4G LTE/LTE-A [1] and remote community (Wireless LAN) frameworks need stress of- FFTs, for example. LTE uplink pre-coding needs Fourier changes from 12 to 2400 without any pressure. However, FFT is a key calculation for all waveform possibilities in the near approach of close to 5G (fifth era bendy correspondence), while the FFT calculation rate is sufficiently immoderate to support a 5G excessively high data rate. Then, the FFT processor wants to maintain a variety of DFTs and immoderate tempo FFTs inside the future multimode base station. For strain of FFTs, several rapid FFT processors have been suggested. In all cases, the number of processors supporting non-pressure DFTs is difficult and fast. The processor supplies the 1536-Component DFT of 4G LTE with the similarly radix-3 device. In the upholds of 48 2,2 m3n, the un-married manner puts the layout of SDF on 6T-RC using a fully fidget (TF) generating element and part-based (STFG). SDF processor focuses on the usage of a solitary table estimate (STAM) for TF age in upholds of 46 2m3n5k. However, due of the limitation of the unmanned pipeline architecture the output is limited to one clock rate. The processors utilise the first-rate component computed computation (PFA) for the assistive 128- to 2048 FFT guide and the 12-within the 1296-component DFT route to minimise TF increases. In all cases, the statistics can not be the same for I/O statistics as for PFA (take a look at in enter and workout consultation outcome). Therefore, the flow rate is limited to at least one clock rate for a future 5G and cannot satisfy the excessive speed need. While ideas for a low-speed, flexible procesor for DFTs and FFTs are difficult to achieve.

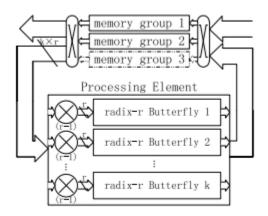

The following factors should be addressed in the construction of a fast processor to enable DFT and FFT: (1) support for 2, 3, 5 and higher radicals gill blocs; (2) TF improve the efficiency of the system and 3) The input for the Free Combat Intelligence is a conspiracy that protects different butterfly equipment from 2, 3, 5 or more radicals and restricts the use of memory owing to the endurance of both DFTs. A memory-based FFT processor supporting 54 modes, including 164096 FFT and 122400 DFT, is suggested for 4G, wireless internet and Destiny 5G and the essential component of the butterfly block is the TF multiplier. And access to knowledge on conspiracy. We have given 8 Radix 2 for each pair, 4 Radix 3/4 for every pair, 4 Radix 5/8 for each peer and Radix16 to reutilize the system assets in life cycle planning. There is a clock cycle of the redesigned throttle body. To support the FFT and the DFT, TF multipliers with various designs were introduced. The strategy was deemed to be the most appropriate for the idea to establish the Advanced Computer Conspirativeness Revolution (CORDIC). Extensive log access pastime completely dependent on plugins and the fundamental strategy for protecting different butterfly devices.

Fig. 1. Architecture of the general memory-based FFT processor.

## PROPOSED SYSTEM:

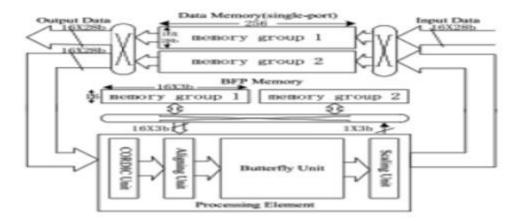

Because the reference technology chooses the reminiscences format with a radix16 butterfly unit. The reference technology in this segment is modified and simplified to support DFT/FFT-sizes with immoderate fading device fees and performance. As shown in Fig. 2, in conjunction with 16 financial institution, the suggested ft processor incorporates: 1) a ping pong remembrance Unmarried port 28-bit reminiscent collection (28-digit statistical width of the genuine 14-bit look and 14-cycle segment photography); 2) rectangular reminiscent gliding point [5] of the styles of facts stored by the company in the BFP; and 3) the difficulty with equipment including CORDIC unit, adapter, butterfly unit and scaled unit. TF increases are performed by the CORDIC unit. The adapting unit and the scaling unit individually lead to the adjustment of BFP requirements and scaling operations.

# FFT PROCESSORS

The short transformation of Fourier and the opposite transformation of Fourier are simple and quick computations to check the discreet transformation of Fourier and the reverse transformation of Fourier. Processing and execution signals – ever fresh opportunities. The OFDM has been and is going to be an effective instrument for calculating FFT throughout the years. OFDM is a strong technique for uplink access based on bandwidth (Engels, 2002; Nee and Prasad, 2000). In most telecommunications systems, a wide variety of OFDM techniques may now be utilised. World Forum, n.), Virtual Video Streaming (DVB), Wireless Proximity Community, Ultra-Wide Band, Multi-Band-Ultra-OFDM (MB-OFDM UWB). In addition to this technique, cable programmes like ADSL or powerline calls are also helpful in general ( percent ). A sender and a recipient must be in each matched frame. IFFT is used for adjusting symbols on the basis of the OFDM frame at the transmission end, while FFT is used for desmodulation of the signal

ISSN: 2233-7857IJFGCN Copyright ©2021SERSC

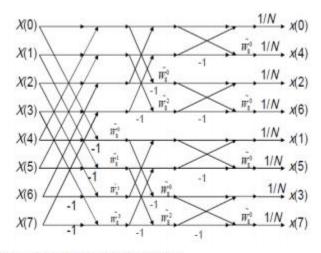

at the receiving end. FFT/OBPF is the OFDM module most often used. We may argue that the main portion of the transmitter is the OFDM frame and IFFT can be utilised to broadcast the Viterbi decoder (Maharatna et al., 2004). Consequently it should strive to achieve significant performance with shadow regions and hysteresis in FFT and IFFT implementation. In most instances, specified justifications are fulfilled within the parameters needed by the current generation of OFDM telephones. You will thus most likely discover that the whole FFT/IFFT is an integrated circuit at big scales (VLSI). OBFT may also apply the technique used in FFT. Furthermore, IFFT may be readily acquired by monitoring the performance of the FFT processor. Therefore, at this point, the spoken communication is largely FFT and there has been no agreement. You may discover a different discreet Fourier exchange and the material it can convey, since in the so called foot factor we notice that the difference between the reported and the former Fourier changes is an aspect deviation and is already known to be a busy subject, split by 1/N.

Fig2. Inverse Fourier Transform.

Far away, progress has progressed surprisingly, remembering that Guglielmo Marconi stated that in 1894 the radio capacity might provide incredible communication with cruises by boat. A number of hundreds and loads of researchers and designers across the globe have developed new theories and uses of extensive improvements. Faraway interchanges may appear since the number one development has an incredibly wide range of uses from TV controllers and mobile to cellular and satellite based television frameworks. In every respect, it changed the way people live. Especially in the last decade, the organisation, with rising fees and via the automated and radio recurrence circuits, developed and mixed methods for organising portable correspondence and clearly indicated energy in chips, has significantly increased. This pattern will keep fast at a much higher speed. The improvements and improvements of the technique significantly helped our fantasies know-how in the quick and reliable transportation every time. In any case, we want to become more involved in such a widespread worldwide experience, as an example, widespread internet browsing and intuitive vision & sound information. One frequent question is: how might we possibly place overflow information across radio lines to suit our needs? This survey should be answered using new distance off broadband access techniques. For example, the forthcoming mobile innovation (1/3) in 3G may provide us with a great deal of record-management of 2Mbps (bits per second). However, it might really stop paying for the information needed through visual and sound media correspondences like HDTV (bright pinnacle television) and video accumulation presently. The development and limitation of the exhibition unmistakably depends on distinct channels of united States. For the frameworks of MIMO-OFDM, channel evaluation takes a key part. Therefore the channel assessment of the MIMO-OFDM Frameworks is important in my study.

#### FIG: 3 PROPOSED FFT PROCESSOR

Input Multiple Multiple output frameworks (MIMO) are devices that can be implemented in a far-reaching fashion. These are devices that show transmitters and receivers. With the MIMO device, immoderate statistics may be obtained. The MIMO and OFDM mix now provides very talented records fees and reliability in widespread communication. The IEEE 802.sixteen WIMAX (world wide Microwave access interoperability) is a recognised flash correspondence that may provide 30-40 Megabit/sec record quotations. The whole new IEEE 802.Sixteen WiMAX evaluation consists of 3GPP (1/3 generation partner task). One of the most important 1/3 period Partnership mission stresses, it is indeed between Nortel and AT&T cellular networks. Wireless AT&T emerges from a long-distance organisation of the IS-136 (TDMA) in the United States in 1998. The RAM has been changed to DRAM to reduce runtime memory using the memory-making plan method, which has 12 memory blocks instead of seventeen. Wireless Nortel networks, in Richardson, Texas, it is actually an R&D concern and a long distance away from Bell Northern study has promoted the idea for the far-flung "all net protocol (IP)" employer who is called the "mobile network.' Nortel Networks The slam is replaced with distinct damage under the suggested concept.

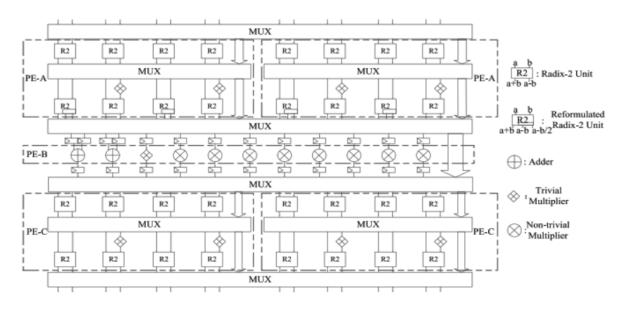

#### **Butterfly Unit:**

The usage of unique butterfly fittings to aid different roots has been proposed. The integrated butterfly block preserves butterfly 2, 3, 4, 5, and 7 of the digital system by re-use of the device adder and propagator. 2D DFT decomposition supports strokes 2, 3, 4, 5, 8, 9, 16 and 25. The high-bottom butterfly block (HRSB) of is supportive with multi-level switching blocks of the route delay functions 2, 3, 4, 5, 8, 9, 12, 15, 16 and 25. The butterfly unit, according to the planning area research in Section 2 and is reformulated for 2, 3, 4, 5, 8 and 16 radical elements. The butterfly block, as illustrated inFigure 3, comprises a two-factor (PE) adjustment device, a PEB block, a PEC block, and many carriers. A base 16, 5/8 bases are the same as a throttle body or 4 bases 3/4 are the same, or 8 bases 2 have comparable duties. It also supports or is accountable for the DFT phase and the A segment of three foundations. PEC Module supports Radixfour's Radix16 FFT or 4 Radix2 Radix8 FFT commitments and supports Part C Radix5 DFT or 2-phase C Radixthree DFT Sports. The adder is transformed into computational power B in radix 5 on the basis of 3, 5, 8 and 16 FFTs.

FIG: 4 BUTTERFLY UNIT IN PROCESSING ELEMENT

Single path delay feedback (SDF) essens is multiplier-measured, the tools are confused with and larger storages are used, the MDC is considered system design, despite the increased rating of the multi-way delay switch [5]. To facilitate the onward flow, use storage transport containers. In this piece we use memory schedule and delay switches to interlude Fourier quickly for various registries, division of a symmetrical frequency and varied frequency rates. Delayed input engineering is more efficient as a type of memory use than matching changes in signal. We want to recreate the jitter Factor using the input characters to compute the FFT to achieve efficiency. This requires a large ROM capacity, which will allow us to keep the input fitting. The FFT/IFFT processors, which destroy the ROM holding fidget components, are considerably smaller to further improve the ROM. For this reason, it uses an issue multiplier. Sooner or later, an advanced multiplier will be employed with two statistical resources to shift and add duties, and capability problems such as the ROM will not halt components. Furthermore, a reconfigurable complex rule multiplier is included to prevent jitter, rather than ROM.

# RESULTS AND DISCUSSION

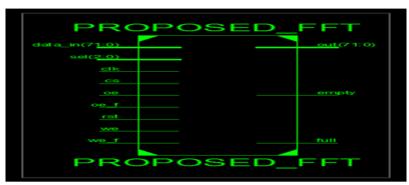

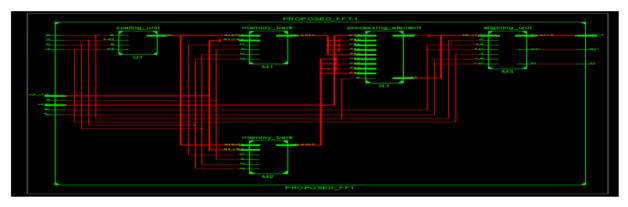

The schematic of the proposed RTL and RTL are shown in the images below and summary of the various borders is shown in the single segments1 und 2.

## RTL BLOCK DIAGRAM

# INTERNAL BLOCK DIAGRAM

# SIMULATION RESULTS

|                   |       |   |        |       |        |         |       |       | 5     | 44. 117 n | IS  |        |       |

|-------------------|-------|---|--------|-------|--------|---------|-------|-------|-------|-----------|-----|--------|-------|

| Name              | Value |   | 400 ns |       | 450 ns |         | 500 r | ıs    |       | 550 ns    |     | 600 ns | 650 n |

| 🕨 📑 out[71:0]     | 15360 | 0 | X      | 40960 | 35840  | 30720 2 | 5600  | 20480 | 15360 | 10240     | X 🚞 | 5120   |       |

| 🗓 empty           | 0     |   |        |       |        |         |       |       |       |           |     |        |       |

| 🖓 full            | 0     |   |        |       |        |         |       |       |       |           |     |        |       |

| 🕨 📷 data_in[71:0] | 80    |   |        |       |        |         | 80    |       |       |           |     |        |       |

| 1 clk             | 0     |   |        |       |        |         | Т     |       |       |           |     |        |       |

| 1 rst             | 0     |   |        |       |        |         |       |       |       |           |     |        |       |

| 16 с              | 1     |   |        |       |        |         |       |       |       |           |     |        |       |

| 16 we             | 0     |   |        |       |        |         |       |       |       |           |     |        |       |

| 1 we_f            | 1     |   |        |       |        |         |       |       |       |           |     |        |       |

| 16 oe_f           | 1     |   |        |       |        |         |       |       |       |           |     |        |       |

| 1 oe              | 1     |   |        |       |        |         |       |       |       |           |     |        |       |

| ▶ 📷 sel[2:0]      | 7     |   |        |       |        |         | 7     |       |       |           |     |        |       |

| Logic Utilization                    | Used | Available | Utilization |  |

|--------------------------------------|------|-----------|-------------|--|

| Number of Slice<br>registers         | 1798 | 595200    | 0%          |  |

| Number of Slice LUTs                 | 7850 | 29700     | 2%          |  |

| Number of fully used<br>LUT-FF pairs | 1308 | 8340      | 15%         |  |

| Number of bonded<br>IOBs             | 130  | 600       | 21%         |  |

| Number of Block<br>RAM?FIFO          | 6    | 1064      | 0%          |  |

| Number of<br>BUFG/BUFGCTRLs          | 1    | 32        | 3%          |  |

| Number of DSP48E1s                   | 228  | 2016      | 11%         |  |

# Table1. Proposed Results Device Utilization Summary

| Tublez Existing Results Derive Officiation Summing |      |           |             |  |  |

|----------------------------------------------------|------|-----------|-------------|--|--|

| Logic Utilization                                  | Used | Available | Utilization |  |  |

| Number of Slice<br>registers                       | 1930 | 595200    | 0%          |  |  |

| Number of Slice LUTs                               | 7906 | 297600    | 2%          |  |  |

| Number of fully used<br>LUT-FF pairs               | 1398 | 8438      | 15%         |  |  |

| Number of bonded<br>IOBs                           | 130  | 600       | 21%         |  |  |

| Number of Block<br>RAM?FIFO                        | 6    | 1064      | 0%          |  |  |

| Number of<br>BUFG/BUFGCTRLs                        | 1    | 32        | 3%          |  |  |

| Number of DSP48E1s                                 | 228  | 2016      | 11%         |  |  |

| Table2. Existing Res | ults Device Uti | lization Summary |

|----------------------|-----------------|------------------|

|----------------------|-----------------|------------------|

# **CONCLUSION**

This article proposes an MDC MIMO FFT/IFFT Processor, based mostly on Radic-R, for the treatment of Ns floods of identical data assets with r = Ns for 100% use of the radix. For a MIMO-OFDM baseband processor such as WiMAX or LTE applications, the suggested approach is economically priced. Where Ns = 4, where Ns = 2048, 512, 256, and 128 are possible. In addition, we suggested a strong memory to utilise reminiscence completely. This significantly decreases the chip area since the memory need in general overwhelms the nearness of the chip in an FFT/IFFT processor. It should be stressed that the configuration suggested is based on an MDC design, it is currently not recommended for the majority of elements, since it uses a low reminiscent rate and computer components such adders and multipliers. Nonetheless, with the help of the proposed memory reserver, encoding engineering is validated in a moderation of the fact that butterflies and multipliers are organised for a 100 percent usage price, in MIMO-OFDM, appropriate for FFT/IFFT processors and that the attributes of easy control provided by the encoding are stored in the proposed scheme during the time suggested.

#### REFERENCES

[1] Larsson, Erik G.; et.al "Massive MIMO for Next Generation Wireless Systems" IEEE Communications Magazine, 52(2), 186-195.

[2] Shaohan Liu and Dake Liu "A High-Flexible Low-Latency Memory-Based FFT Processor for 4G, WLAN, and Future 5G" IEEE Transactions on VERY Large Scale Integration (VLSI) Systems, 2018, 1-13.

[3] Felipe Minotta, et.al "Automated Scalable Address Generation Patterns for 2-Dimensional Folding Schemes in Radix-2 FFT Implementations" Electronics 2018, 7, 33; doi:10.3390/electronics7030033, 1-18 [4] Gelaye Geresu and Lamessa Dingeta "Area-Efficient 128- to 2048/1536-Point Pipeline FFT Processor for LTE and Mobile Wimax Systems" International Journal of VLSI System Design and Communication System, ISSN 2322-0929 Vol.04, Issue.13, December-2016, Pages: 1487-1491.

[5] 'Wen-Chang Yeh' & 'Chein-Wei Jen' "High-Speed and Low-Power Split-Radix FFT" IEEE TRANSACTIONS ON SIGNAL PROCESSING, VOL. 51, NO. 3, MARCH 2003, 864-874.

[6] Z Wang, X Liu, Bingsheng He, Feng Yu "A Combined SDC-SDF Architecture for Normal I/O Pipelined Radix2 FFT" IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS 2013, 1-5pg.

[7] S. He, M. Torkelson, A new approach to pipeline FFT processor, in: Proceedings of IPPS'96, The 10th International Parallel Processing Symposium, 1996, Honolulu, HI, IEEE, 1996, pp. 766–770.

[8] Y. Jung, H. Yoon, J. Kim, New efficient FFT algorithm and pipeline implementation results for FDM/DMT applications, IEEE Trans. Consum. Electron. 49 (1) (2003) 14–20.

[9] O. Jung-Yeol, L. Myoung-Seob, New radix-2 to the 4th power pipeline FFT processor, IEICE Trans. Electron. 88 (8) (2005) 1740–1746.

[10] A. Cortés, I. Vélez, J.F. Sevillano, Radix FFTs: matricial representation and SDC/ SDF pipeline implementation, IEEE Trans. Signal Process. 57 (7) (2009)2824–2839.

[11] C.-L. Wey, S.-Y. Lin, W.-C. Tang, Efficient memorybased FFT processors for OFDM applications, in: 2007 IEEE International Conference on Electro/ Information Technology, Chicago, IL, IEEE, 2007, pp. 345–350.

[12] K.-J. Yang, S.-H. Tsai, G.C. Chuang, MDC FFT/IFFT processor with variable length for MIMO-OFDM systems, IEEE Trans. Very Large Scale Integr. Syst. 21 (4) (2013) 720–731.